Динамическая оперативная память. Регенерация динамической памяти

Запоминающая ячейка динамического типа хранит информацию в виде заряда емкости. Ток утечки обратно смещенного p-n перехода составляет не более 10-10 A (0,1 нA ), а емкость - 0,1..0,2 пФ, следовательно постоянная времени разряда - более 1 мС . Поэтому через каждые 1..2 мС требуется производить подзаряд емкостей запоминающих элементов - регенерацию динамической памяти.

В динамических ОЗУ чаще используется т.н. "строчная регенерация", при которой в одном цикле регенерируются все элементы, расположенные в одной строке прямоугольной матрицы накопителя. Следует отметить, что любое обращение к запоминающей ячейке (запись или чтение) осуществляет ее регенерацию и одновременно регенерирует все ячейки, расположенные в той же строке накопителя.

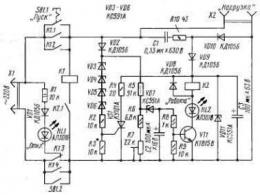

Рис. 1. Управление регенерацией динамической памяти

Однако, при работе ОЗУ в составе МПС в общем случае нельзя дать гарантию, что в течение 2мС произойдет обращение ко всем строкам накопителя, т.к. поток адресов является случайным. Для обеспечения гарантированной сохранности информации в динамическом ОЗУ при работе МПС вводятся специальные циклы регенерации - обращения к ОЗУ по последовательным адресам строк.

В большинство динамических ОЗУ адрес ячейки подается за два приема : сначала - адрес строки, который запоминается во внутреннем регистре ОЗУ, потом по тем же линиям - адрес столбца. Каждая передаваемая по мультиплексированным линиям часть адреса сопровождается соответствующим управляющим сигналом (RAS, CAS).

Для регенерации накопителя достаточно провести обращение только к последовательным строкам - каждый цикл обращения для регенерации может состоять только из передачи адреса строки. Поэтому для полной регенерации накопителя объемом 16K (матрица 128 ´ 128) достаточно 128 тактов. Накопители большего объема реализуют на неквадратных матрицах, чтобы уменьшить число строк и сократить время регенерации. Так, накопитель объемом 64K имеет матрицу 128 ´ 512.

Различают несколько способов организации регенерации динамических ОЗУ в МПС.

Регенерация "по таймеру" . В состав МПС вкл ючается таймер регенерации, который каждые 2 мС формирует сигнал, блокирующий обращение МП к памяти и запускающий процедуру регенерации. Схема управления регенерацией включает в себя счетчик адреса регенерации, триггер регенерации и мультиплексор адреса.

Недостатком такого способа регенерации является значительная потеря времени на регенерацию - до нескольких процентов времени работы МПС, причем это время может возрастать с ростом объема памяти МПС. Таким образом, использование метода регенерации по таймеру снижает производительность МПС, т.к. при выполнении регенерации МП пребывает в состоянии ожидания.

"Прозрачная" регенерация . Главным достоинством метода прозрачной регенерации является отсутствие простоев МП при регенерации ОЗУ, поскольку для регенерации выбираются такие моменты времени, когда МП не занимает системную шину. Однажды начав регенерацию, совсем не обязательно проводить ее полностью. Циклы регенерации могут чередоваться с процессорными циклами, главное, чтобы процесс регенерации накопителя завершился за время, не превышающее 2 мС . Многие МП формируют специальные сигналы, отмечающие занятость шины. Эти сигналы можно использовать для управления триггером регенерации. Если МП (например, i8080) не формирует сигнала занятости магистрали, то такой сигнал можно сформировать специальной внешней схемой.

Так, в машинном цикле МП i8080 могут появляться такты T4, T5, в которых МП не занимает системную шину. Эти моменты времени можно выделять специальной схемой и использовать для регенерации.

Микропроцессор Z80 имеет встроенный счетчик регенерации и обеспечивает этот процесс самостоятельно параллельно с внутренней обработкой информации на кристалле.

В большинстве МП не предусмотрены средства обеспечения регенерации, т.к. в МПС может и отсутствовать динамическая память. Однако, в составе микропроцессорных комплектов выпускаются специальные БИС контроллеров регенерации. В качестве примера кратко рассмотрим структуру и функционирование БИС К1818ВТ03 - "Контроллер динамической памяти". Ниже показана структура БИС 565РУ5 (64К´ 1), а на рис.3 временная диаграмма ее работы.

Рис. 2 . Структура БИС динамического ОЗУ

БИС динамических ЗУ имеют объемы от 16К´ 1 (565РУ3) до 1М´ 1 (..РУ9 ), но имеют одинаковую структуру и линии управления (за исключением числа адресных).

Рис. 3 . Временная диаграмма работы БИС динамического ОЗУ

Из рисунков следует, что адрес ячейки подается в ОЗУ последовательно двумя порциями по одним и тем же линиям в сопровождении управляющих сигналов RAS\ (строб адреса строки) и CAS\ (строб адреса столбца). Поэтому адрес на системной шине, формируемый МП, должен мультиплексироваться, одновременно вырабатываться управляющие сигналы RAS и CAS.

Кристалл ОЗУ бывает выбран только при условии RAS = CAS = 0, что позволяет осуществлять селекцию блоков по двум координатам.

Контроллер динамической памяти (КДП) обеспечивает мультиплексирование адреса системной шины, выработку управляющих сигналов CAS и RAS (для селекции модулей ОЗУ), а также внутреннюю (по таймеру) или внешнюю (прозрачную) регенерацию.

Структурная схема контроллеравключает в себя :

· буферные схемы Буф.1,2,3 для подключения системной шины адреса и управления;

· счетчик адреса регенерации;

· мультиплексоры MUX1,2;

· схему управления с тактовым генератором, таймером и триггером регенерации, арбитром и логической схемой L для формирования управляющих сигналов.

КДП обеспечивает преобразование сигналов системной шины МПС в сигналы управления динамическим ОЗУ, причем может работать в двух режимах : "16/64" (на память 16K или 64K соответственно). В режиме "16" две старшие линии адреса используются для формирования одного из сигналов RAS\, в режиме "64" КДП может управлять двумя банками по 64K, причем сигнал RAS появляется на одном из выходов RAS0 или RAS1 - в зависимости от состояния линии RAS3\/B0, которая в режиме "64" становится входом, определяющим номер банка ОЗУ.

Регенерация может осуществляться в двух режимах - внутреннем и внешнем. Если вход REFR остается неактивным 10..16 мкС , то формируется запрос на цикл регенерации от внутреннего таймера, причем в случае конфликта арбитр отдает предпочтение циклу памяти. Таким образом, и при регенерации по таймеру используются свободные такты шины. При внешней регенерации запрос должен быть сформирован на входе REFR.

Сигнал PCS - "Защищенный выбор кристалла" отличается от традиционного CS тем, что если PCS сформирован, то цикл ЗУ аннулировать нельзя.

Рис. 4 . Контроллер динамического ОЗУ

RD, WR - запросы на циклы чтения и записи соответственно.

X0, X1 - выводы для подключения кварцевого резонатора при работе с внутренним генератором. При работе с внешним генератором на вход X0 подается высокий потенциал, а на X1 - частота CLK внешнего генератора.

Выходной сигнал SACK\ вырабатывается КДП в начале цикла обращения к памяти. Если запрос от МП приходится на цикл регенерации, то SACK\ задерживается до начала цикла чтения/записи.

Выходной сигнал XACK\ ("Готовность данных") вырабатывается в конце цикла чтения/записи.

Сигналы SACK\ и XACK\ можно использовать для управления потенциалом на входе READY микропроцессора.

В некоторых, достаточно редких частных случаях, можно воспользоваться способом регенерации "размещением данных" . Так, если, например, память изображения дисплея является составной частью единого ОЗУ МПС и МП регулярно обращается в эту область для поддержания изображения на экране, то достаточно расположить область ОЗУ дисплея в памяти МПС таким образом, чтобы она "перекрывала" все строки накопителя (достигается соответствующим подбором адресов), чтобы каждое обращение к области ОЗУ дисплея, помимо регенерации изображения, регенерировала и всю память МПС.

Классификация типов памяти

Следует различать классификацию памяти и классификацию запоминающих устройств (ЗУ). Первая классифицирует память по функциональности, вторая же - по технической реализации. Здесь рассматривается первая - таким образом, в неё попадают как аппаратные виды памяти (реализуемые на ЗУ), так и структуры данных, реализуемые в большинстве случаев программно.

Доступные операции с данными

* Память только для чтения (read-only memory, ROM)

* Память для чтения/записи

Память на программируемых и перепрограммируемых ПЗУ (ППЗУ и ПППЗУ) не имеет общепринятого места в этой классификации. Её относят либо к подвиду памяти «только для чтения», либо выделяют в отдельный вид.

Также предлагается относить память к тому или иному виду по характерной частоте её перезаписи на практике: к RAM относить виды, в которых информация часто меняется в процессе работы, а к ROM - предназначенные для хранения относительно неизменных данных.

Энергозависимость

· Энергонезависимая память (англ. nonvolatile storage) - память, реализованная ЗУ, записи в которых не стираются при снятии электропитания. К этому типу памяти относятся все виды памяти на ПЗУ и ППЗУ;

· Энергозависимая память (англ. volatile storage) - память, реализованная ЗУ, записи в которых стираются при снятии электропитания. К этому типу памяти относятся память, реализованная на ОЗУ, кэш-память.

o Статическая память (англ. static storage) - энергозависимая память, которой для хранения информации достаточно сохранения питающего напряжения;

o Динамическая память (англ. dynamic storage) - энергозависимая память, в которой информация со временем разрушается (деградирует), и, кроме подачи электропитания, необходимо производить её периодическое восстановление (регенерацию).

1)Энергонезависимая память (англ. Non Volatile Random Access Memory, NVRAM) - подгруппа более общего класса энергонезависимых запоминающих устройств; разница заключается в том, что в отличие от жестких дисков, устройства NVRAM предлагают прямой доступ.

В более общем смысле, энергонезависимая память - любое устройство компьютерной памяти, или его часть, сохраняющее данные вне зависимости от подачи питающего напряжения. Однако подпадающие под это определение носители информации, ПЗУ, ППЗУ, устройства с подвижным носителем информации (диски, ленты) и другие носят свои, более точные названия.

Поэтому термин «энергонезависимая память» чаще всего употребляется более узко, по отношению к полупроводниковым БИС запоминающих устройств, которая обычно выполняется энергозависимой, и содержимое которой при выключении обычно пропадает. Под понятие энергонезависимой памяти подпадают по сути энергозависимая память, „энергонезависимость“ которой обеспечивается применением технологией с «ускользающе малым потреблением» (например) вкупе с подпиткой от миниатюрной батарейки или SSD.

Например, часы на системной плате персонального компьютера или ОЗУ современного RAID-контроллера.

2)Эне́ргозави́симая па́мять (англ. Volatile memory) - компьютерная память, которая требует постоянного использования электропитания для возможности удерживать записанную на неё информацию. Эта особенность является ключевым отличием энергозависимой памяти от энергонезависимой - последняя сохраняет записанную на неё информацию даже после прекращения подачи электропитания на неё. Энергозависимая память также изредка называется вре́менной памятью (англ. temporary memory).

Подавляющее большинство современных видов оперативной памяти с произвольным доступом являются энергозависимыми. Сюда относятся динамическая (DRAM) и статическая (SRAM) память с произвольным доступом. Ассоциативная память и DPRAM как правило реализуются через энергозависимую память. К ранним технологиям энергозависимой памяти относятся память на линиях задержки и запоминающая электронно-лучевая трубка.

2.1)Статическая оперативная память с произвольным доступом (SRAM, static random access memory) - полупроводниковая оперативная память, в которой каждый двоичный или троичный разряд хранится в схеме с положительной обратной связью, позволяющей поддерживать состояние без регенерации, необходимой в динамической памяти (DRAM). Тем не менее, сохранять данные без перезаписи SRAM может только пока есть питание, то есть SRAM остается энергозависимым типом памяти. Произвольный доступ (RAM - random access memory) - возможность выбирать для записи/чтения любой из битов (тритов) (чаще байтов (трайтов), зависит от особенностей конструкции), в отличие от памяти с последовательным доступом (SAM - sequential access memory).

Преимущества

Быстрый доступ. SRAM - это действительно память произвольного доступа, доступ к любой ячейке памяти в любой момент занимает одно и то же время.

Простая схемотехника - SRAM не требуются сложные контроллеры.

Возможны очень низкие частоты синхронизации, вплоть до полной остановки синхроимпульсов.

Низкое энергопотребление.

Недостатки

Невысокая плотность записи (шесть-восемь элементов на бит, вместо двух у DRAM).

Вследствие чего - дороговизна килобайта памяти.

Тем не менее, высокое энергопотребление не является принципиальной особенностью SRAM, оно обусловлено высокими скоростями обмена с данным видом внутренней памяти процессора. Энергия потребляется только в момент изменения информации в ячейке SRAM.

Применение

SRAM применяется в микроконтроллерах и ПЛИС, в которых объём ОЗУ невелик (единицы килобайт), зато нужны низкое энергопотребление (за счёт отсутствия сложного контроллера динамической памяти), предсказываемое с точностью до такта время работы подпрограмм и отладка прямо на устройстве.

В устройствах с большим объёмом ОЗУ рабочая память выполняется как DRAM. SRAM’ом же делают регистры и кеш-память.

2.2)Динамическая память с произвольным доступом) - тип энергозависимой полупроводниковой памяти с произвольным доступом; DRAM широко используемая в качестве оперативной памяти современных компьютеров, а также в качестве постоянного хранилища информации в системах, требовательных к задержкам.

Физически DRAM состоит из ячеек, созданных в полупроводниковом материале, в каждой из которых можно хранить определённый объём данных, строку от 1 до 4 бит. Совокупность ячеек такой памяти образуют условный «прямоугольник», состоящий из определённого количества строк и столбцов. Один такой «прямоугольник» называется страницей, а совокупность страниц называется банком. Весь набор ячеек условно делится на несколько областей.

Как запоминающее устройство, DRAM представляет собой модуль памяти различных конструктивов, состоящий из электрической платы, на которой расположены микросхемы памяти и разъёма, необходимого для подключения модуля к материнской плате.

Принцип действия

Физически DRAM-память представляет собой набор запоминающих ячеек, которые состоят из конденсаторов и транзисторов, расположенных внутри полупроводниковых микросхем памяти.

При отсутствии подачи электроэнергии к памяти этого типа происходит разряд конденсаторов, и память опустошается (обнуляется). Для поддержания необходимого напряжения на обкладках конденсаторов ячеек и сохранения их содержимого, их необходимо периодически подзаряжать, прилагая к ним напряжения через коммутирующие транзисторные ключи. Такое динамическое поддержание заряда конденсатора является основополагающим принципом работы памяти типа DRAM. Конденсаторы заряжают в случае, когда в «ячейку» записывается единичный бит, и разряжают в случае, когда в «ячейку» необходимо записать нулевой бит.

Важным элементом памяти этого типа является чувствительный усилитель-компаратор (англ. sense amp), подключенный к каждому из столбцов «прямоугольника». Он, реагируя на слабый поток электронов, устремившихся через открытые транзисторы с обкладок конденсаторов, считывает всю строку целиком. Именно строка является минимальной порцией обмена с динамической памятью, поэтому обмен данными с отдельно взятой ячейкой невозможен.

Регенерация

В отличие от быстрой, но дорогой статической памяти типа SRAM (англ. static random access memory), которая является конструктивно более сложным и более дорогим типом памяти и используется в основном в кэш-памяти, медленная, но дешёвая память DRAM изготавливается на основе конденсаторов небольшой ёмкости, которые быстро теряют заряд, поэтому информацию приходится обновлять через определённые промежутки времени во избежание потерь данных. Этот процесс называется регенерацией памяти. Он реализуется специальным контроллером, установленным на материнской плате или же на кристалле центрального процессора. На протяжении времени, называемого шагом регенерации, в DRAM перезаписывается целая строка ячеек, и через 8-64 мс обновляются все строки памяти.

Процесс регенерации памяти в классическом варианте существенно тормозит работу системы, поскольку в это время обмен данными с памятью невозможен. Регенерация, основанная на обычном переборе строк, в современных типах DRAM не применяется. Существует несколько более экономичных вариантов этого процесса - расширенный, пакетный, распределённый; наиболее экономичной является скрытая (теневая) регенерация.

Среди новых технологий регенерации - PASR (англ. Partial Array Self Refresh), применяемый компанией Samsung в чипах памяти SDRAM с низким уровнем энергопотребления. Регенерация ячеек выполняется только в период ожидания в тех банках памяти, в которых имеются данные.

Параллельно с этой технологией реализуется метод TCSR (англ. Temperature Compensated Self Refresh), который предназначен для регулировки скорости процесса регенерации в зависимости от рабочей температуры.

Характеристики памяти DRAM

Основными характеристиками DRAM являются рабочая частота и тайминги.

При обращении к ячейке памяти контроллер памяти задаёт номер банка, номер страницы в нём, номер строки и номер столбца и на все эти запросы тратится время, помимо этого довольно большой период уходит на открытие и закрытие банка после самой операции. На каждое действие требуется время, называемое таймингом.

Основными таймингами DRAM являются: задержка между подачей номера строки и номера столбца, называемая временем полного доступа (англ. RAS to CAS delay), задержка между подачей номера столбца и получением содержимого ячейки, называемая временем рабочего цикла (англ. CAS delay), задержка между чтением последней ячейки и подачей номера новой строки (англ. RAS precharge). Тайминги измеряются в наносекундах или тактах, и чем меньше величина этих таймингов, тем быстрее работает оперативная память.

Типы DRAM

На протяжении долгого времени разработчиками создавались различные типы памяти. Они обладали разными характеристиками, в них были использованы разные технические решения. Основной движущей силой развития памяти было развитие компьютеров и центральных процессоров. Постоянно требовалось увеличение быстродействия и объёма оперативной памяти.

Совокупность ячеек такой памяти образуют условный «прямоугольник», состоящий из определённого количества строк и столбцов . Один такой «прямоугольник» называется страницей , а совокупность страниц называется банком . Весь набор ячеек условно делится на несколько областей.

Как запоминающее устройство , DRAM представляет собой модуль памяти различных конструктивов, состоящий из электрической платы, на которой расположены микросхемы памяти и разъёма, необходимого для подключения модуля к материнской плате.

Принцип действия

Принцип действия чтения DRAM для простого массива 4×4

Принцип действия записи DRAM для простого массива 4×4

Физически DRAM-память представляет собой набор запоминающих ячеек , которые состоят из конденсаторов и транзисторов , расположенных внутри полупроводниковых микросхем памяти.

Первоначально микросхемы памяти выпускались в корпусах типа DIP (к примеру, серия К565РУхх), далее они стали производиться в более технологичных для применения в модулях корпусах.

На многих модулях SIMM и подавляющем числе DIMM устанавливалась SPD (Serial Presence Detect) - небольшая микросхема памяти EEPROM, хранящяя параметры модуля (ёмкость, тип, рабочее напряжение, число банков, время доступа и т. п.), которые программно были доступны как оборудованию, в котором модуль был установлен (применялось для автонастройки параметров), так и пользователям и производителям.

Модули SIPP

Модули типа SIPP (Single In-line Pin Package) представляют собой прямоугольные платы с контактами в виде ряда маленьких штырьков. Этот тип конструктивного исполнения уже практически не используется, так как он далее был вытеснен модулями типа SIMM.

Модули SIMM

Модули типа SIMM (Single In-line Memory Module) представляют собой длинные прямоугольные платы с рядом контактных площадок вдоль одной из её сторон. Модули фиксируются в разъёме (сокете) подключения с помощью защёлок, путём установки платы под некоторым углом и нажатия на неё до приведения в вертикальное положение. Выпускались модули на 4, 8, 16, 32, 64, 128 Мбайт.

Наиболее распространены 30- и 72-контактные модули SIMM.

Модули DIMM

Модули типа DIMM (Dual In-line Memory Module) представляют собой длинные прямоугольные платы с рядами контактных площадок вдоль обеих её сторон, устанавливаемые в разъём подключения вертикально и фиксируемые по обоим торцам защёлками. Микросхемы памяти на них могут быть размещены как с одной, так и с обеих сторон платы.

Модули памяти типа SDRAM наиболее распространены в виде 168-контактных DIMM-модулей, памяти типа DDR SDRAM - в виде 184-контактных, а модули типа DDR2, DDR3 и FB-DIMM SDRAM - 240-контактных модулей.

Модули SO-DIMM

Для портативных и компактных устройств (материнских плат форм-фактора Mini-ITX , лэптопов , ноутбуков , таблетов и т. п.), а также принтеров, сетевой и телекоммуникационной техники и пр. широко применяются конструктивно уменьшенные модули DRAM (как SDRAM, так и DDR SDRAM) - SO-DIMM (Small outline DIMM) - аналоги модулей DIMM в компактном исполнении для экономии места.

Здравствуйте, уважаемые читатели блога Help начинающему пользователю компьютера. Сегодня мы опишем физическую и логическую организацию динамической памяти DRAM.

Физически память DRAM

(Dynamic RAM - DRAM)

состоит из ячеек. Совокупность ячеек

DRAM-памяти образуют матрицу, в которую входит определённое количество строк и столбцов. Матрицу ячеек еще называют страницей. Совокупность страниц называют банком.

Для образования одной ячейки используется электронная схема, в которую входит один транзистор и один конденсатор (это простейшая схема). Конденсатор в течении некоторого промежутка способен сохранять электрический заряд (заряды в конденсаторах стекают, поэтому память получила своё название динамическая). Присутствие или отсутствие заряда на конденсаторе дает бит информации (1 или 0) – единицу информации. Таким образом, чтобы записать в ячейку бит информации в виде логической единицы, необходимо зарядить конденсатор. Чтобы получить логический нуль конденсатор разряжают.

При считывании данных каждый конденсатор разряжается, поэтому его необходимо зарядить до предыдущего значения. Кроме того, конденсаторы сохраняют заряд только на протяжении определенного промежутка времени и время от времени нуждаются в подзарядке (чтобы не терялись данные). Для этого используется регенерация электрического заряда конденсатора . Процесс регенерации сочетается с процессом считывания информации из ячеек DRAM. Но когда в промежутке длительного времени обращение к ячейке не происходит (конденсаторы разряжаются), контроллер памяти (обычно встраиваемый в набор микросхем системной платы, однако он может быть встроен и в процессор) периодически обращается ко всем ячейкам в микросхемах памяти и восстанавливает данные. Процесс регенерации замедляет роботу системы, поскольку при регенерации памяти обмен данными с памятью невозможен.

По логике организации DRAM-память может быть асинхронной (обмен данными, подача адресов выполняются в произвольные моменты времени) и синхронной (имеется внешний синхронный сигнал, к импульсам которого привязаны моменты подачи адресов и обмена данными).

Динамическая оперативная память на данный момент наиболее широко используется в современных ПК.

Причинами такой популярности стали:

- Компактность DRAM. Ячейки динамической памяти очень плотно упакованы, что позволяет организовать память большой емкости.

- Дешевизна модулей памяти. Использованием схемы с одним конденсатором и транзистором в качестве ячейки памяти дешевле по сравнению с статической памятью (где в качестве ячейки памяти выступает триггер, который включает в себя несколько транзисторов).

Стоит отметить, что динамическая память имеет ряд минусов:

Динамическая память по сравнению с памятью статической работает медленнее (связано с затратой времени на зарядку и разрядку конденсаторов). К минусам относится необходимость регенерации заряда конденсатора (цикл регенерации по длительности занимает несколько тактов центрального процессора), поскольку при регенерации периодически приостанавливаются все операции с памятью.

Память типа ROM

ОРГАНИЗАЦИЯ ОП.

Оперативная память - это рабочая область для процессора компьютера.

В компьютерах используются запоминающие устройства трех основных типов:

1. ROM (Read Only Memory ) – ПЗУ, не способное выполнять операцию записи данных.

2. DRAM (Dynamic Random Access Memory ) - динамическое запоминающее устройство с произвольным порядком выборки.

3. SRAM (Static RAM ) - статическая оперативная память.

В памяти типа ROM (Read Only Memory), или ПЗУ (постоянное запоминающее устройство), данные можно только хранить, изменять их нельзя. Именно поэтому такая память используется только для чтения данных. ROM также часто называется энергонезависимой памятью , потому что любые данные, записанные в нее, сохраняются при выключении питания. Поэтому в ROM помещаются команды запуска ПК, т.е. программное обеспечение, которое загружает систему.

Динамическая оперативная память (Dynamic RAM - DRAM) используется в большинстве систем оперативной памяти современных ПК. Основное преимущество памяти этого типа состоит в том, что ее ячейки упакованы очень плотно, т.е. в небольшую микросхему можно упаковать много битов, а значит, на их основе можно построить память большой емкости. Ячейки памяти в микросхеме DRAM - это крошечные конденсаторы, которые удерживают заряды. Наличием или отсутствием зарядов кодируются биты. Проблемы, связанные с памятью этого типа, вызваны тем, что она динамическая, т.е. должна постоянно регенерироваться, так как в противном случае электрические заряды в конденсаторах памяти будут “стекать” и данные будут потеряны.

Кэш"память " SRAM

Память SRAM в отличие от динамической оперативной памяти (DRAM), для сохранения ее содержимого не требует периодической регенерации. SRAM имеет более высокое быстродействие, чем DRAM, и может работать на той же частоте, что и современные ЦП. Однако для хранения каждого бита в конструкции SRAM используется кластер из шести транзисторов. Использование транзисторов без каких либо конденсаторов означает, что нет необходимости в регенерации.

Оперативная память всегда строится из отдельных модулей памяти, которые имеют свое собственное электронное обрамление (т.е. устройства, обеспечивающие запись, выборку, чтение). Структура модуля памяти определяется способом организации ОП (способ адресации). Существует 3 разновидности организации оперативной памяти:

1) адресная память

2) память со стековой организацией

3) ассоциативная организация ОП

С точки зрения функционального построения, любое ЗУ этого типа представляет собой некоторый массив элементов памяти. Структурные элементы памяти образуют ячейки памяти. Ширина ячеек – ширина выборки из памяти.

1) В адресной памяти, размещение и поиск информации в запоминающем массиве, базируется на основе номера (адреса). Массив запоминания элементов содержит N n-разрядных слов, которые пронумерованы (0…N-1). Электронное обрамление включает в себя регистры для хранения адреса памяти, регистр информации (само слово), схемы адресной выборки (адресации), разрядные усилители для чтения и записи.

Цикл работы памяти инициируется сигналом обращения к памяти и операцией (ЗП/ЧТ). При инициировании обращения производится дешифрация адреса схемы адресной выборки. Если задана операция чтения, то активизируется усилитель считывания и информация через него предается в регистр информации памяти. Если память требует динамической регенерации, то после регистра информации памяти все поступает в регистр адреса памяти. Если происходит операция записи, то активизируется усилитель записи, который обеспечивает запись из регистра информации памяти в нужное место памяти.

2) В стековой организации запись нового слова, поступившего с входной информационной шиной, производится в верхнюю (нулевую) ячейку- которая является выходной информационной шиной, при этом все ранее записанные слова (включая слово в ячейке 0) сдвигаются вниз, в соседние ячейки, номера которых на единицу больше. Считывание возможно только из верхней (нулевой) ячейки памяти. Основной режим – это считывание с удалением. Таким образом, ячейка N-1 – дно стека, а ячейка 0 – вершина.

Обычно аппаратный стек снабжается счетчиком стека СчСт, показывающим общее количество занесенных в память слов (СчСт = 0 – стек пустой). При заполнении стека полностью он запрещает дальнейшие операции записи. Стековая организация данных возможна и на обычной адресной памяти с произвольным обращением (программный стек). Для организации стека в этом случае необходима еще одна ячейка памяти (регистр), в которой всегда хранится адрес вершины стека и которая называется указателем стека . Обычно в качестве указателя стека используют один из внутренних регистров процессора. Кроме этого, требуется соответствующее программное обеспечение.

В отличие от аппаратного стека данные, размещенные в программном стеке, при записи нового числа или считывании не перемещаются. Запись каждого нового слова осуществляется в ячейку памяти, следующую по порядку за той, адрес которой содержится в указателе стека. При этом содержимое указателя стека увеличивается на единицу. Таким образом, в программном стеке перемещаются не данные, а вершина стека. При считывании слова из стека происходит обратный процесс. Слово считывается из ячейки, адрес которой находится в указателе стека, после чего содержимое указателя стека уменьшается на единицу.

3) В ассоциативной памяти поиск информации происходит не по адресу, а по ее содержанию. Под содержанием информации в данном случае понимается побитовый состав записанного двоичного слова. При этом ассоциативный запрос также представляет собой двоичный код с определенным побитовым составом. Поиск по ассоциативному запросу происходит параллельно во времени для всех ячеек ЗМ и представляет собой операцию сравнения содержимого разрядов регистра запроса с содержимым соответствующих разрядов ячеек памяти. Для организации такого поиска все ЗЭ ЗМ снабжены однобитовыми процессорами, поэтому в ряде случаев память такого типа рассматривают как многопроцессорную систему.

Ассоциативный поиск можно реализовать и в компьютере с обычной адресной памятью, последовательно вызывая записанные в ячейки памяти слова в процессор и сравнивая их с некоторым ассоциативным признаком (шаблоном).

Контроль четности и коды коррекции ошибок (ECC)

Факторы программных ошибок в памяти:

Скачки в энергопотреблении или шум на линии .

Использование неверного типа или параметра быстродействия памяти .

Статические разряды .

Ошибки синхронизации .

Тепловыделение .

Для повышения отказоустойчивости в компьютерах применяются методы контроля четности и коды коррекции ошибок (ECC ).

В методе контроля четности информация в банках памяти хранится фрагментами по 9 бит, причем восемь из них (составляющих один байт) предназначены собственно для данных, а девятый является битом четности (parity ). Использование девятого бита позволяет схемам управления памятью на аппаратном уровне контролировать целостность каждого байта данных. Если обнаруживается ошибка, работа компьютера останавливается и на экран выводится сообщение о неисправности. Если вы работаете на компьютере под управлением Windows или OS/2, то при возникновении ошибки контроля четности сообщение, возможно, не появится, а просто произойдет блокировка системы.

Технология контроля четности не позволяет исправлять системные ошибки, однако дает возможность их обнаружить пользователю компьютера, что имеет следующие преимущества:

контроль четности оберегает от последствий проведения неверных вычислений на базе некорректных данных;

контроль четности точно указывает на источник возникновения ошибок, помогая разобраться с проблемой и улучшая степень эксплуатационной надежности компьютера.

Коды коррекции ошибок (Error Correcting Code - ECC) позволяют не только обнаружить ошибку, но и исправить ее в одном разряде. В случае ошибки в одном разряде ПК может работать без прерывания, причем данные не будут искажены. Коды коррекции ошибок в большинстве ПК позволяют только обнаруживать, но не исправлять ошибки в двух разрядах. Данный тип ECC получил название SEC_DED (single_bit error_correction double_bit error detection - одноразрядная коррекция, двухразрядное обнаружение ошибок). В кодах коррекции ошибок этого типа для каждых 32 бит требуется дополнительно семь контрольных разрядов при 4_байтовой и восемь - при 8_байтовой организации (64_разрядные процессоры Athlon/Pentium). Для использования кодов коррекции ошибок необходим контроллер памяти, вычисляющий контрольные разряды при операции записи в память. При чтении из памяти такой контроллер сравнивает прочитанные и вычисленные значения контрольных разрядов и при необходимости исправляет испорченный бит (или биты).